近期,微电子学院姚镭教授团队在高压(>10V)脉冲发生器IC研究领域取得重要进展。相关工作以“A 15.4V Fully-Integrated Energy-Efficient Pulse Generator in Standard 0.18μm CMOS (基于0.18μm标准CMOS工艺的15.4V全集成高效率电压脉冲发生器)”为题,发表于IEEE Transactions on Circuits and Systems II: Express Briefs。

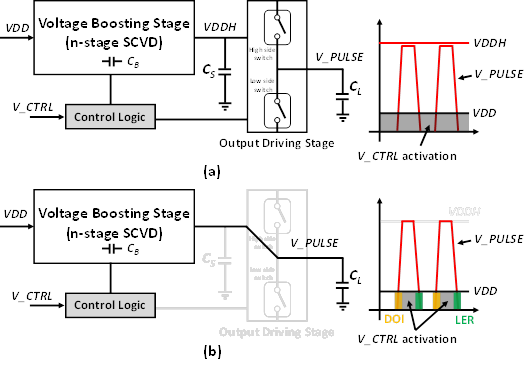

在很多MEMS传感器应用中,大于10V的高压脉冲发生器是一个重要的功能模块,如提供高压偏置、机械驱动和各种能量转换发射等。在传感器应用领域,传统的高压脉冲发生器架构是采用基于开关电容电压倍增器(SCVD)的电荷泵和高压开关来实现(图1(a))。这种架构的主要缺点有两个:一是由于高压开关需要高压晶体管或大阻值电阻网络会导致芯片面积非常大;二是需要一个片外电荷存储电容以降低脉冲开关时的电压压降。为了解决两个缺点,如图1(b)所示基于纯SCVD的高压脉冲发生器结构被提出,但是纯SCVD结构的脉冲发生器能量利用效率非常低(10-20%),导致实用性差。基于这样的背景,姚镭教授团队提出了一种双模SCVD结构(D-SCVD),通过在脉冲上升过程中调制脉冲发生器的输出阻抗(DOI)以及在脉冲下降沿回收负载电容上的能量(LER)这两种创新方法大大提高了纯SCVD高压脉冲发生器的能量利用效率。实验结果表明,该高压脉冲发生器的能量利用效率达到43.5%,使纯SCVD结构的脉冲发生器达到可进入实用化的阶段。

图1.(a)传统结构的高压脉冲发生器架构 (b)纯SCVD的高压脉冲发生器架构

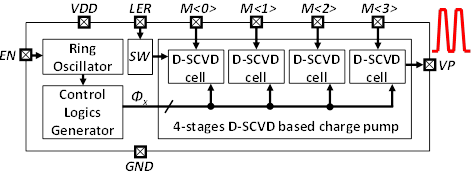

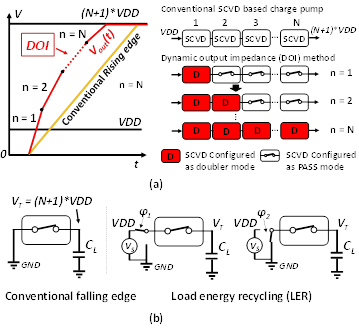

该研究介绍了这种高压脉冲发生器的工作原理、电路设计和实验验证的全过程。该电路由四个双模开关电容电压倍增器(D-SCVD)模块级联组成,并辅以时钟发生器和辅助逻辑电路帮助完成模式切换等工作(图2)。作为这种高压脉冲发生器的核心部分,四级D-SCVD级联结构能够动态配置级数以实现输出阻抗的动态调节,并实现输入输出的直连以回收负载电容中的电荷。该发生器具有动态输出阻抗(DOI)和负载能量回收(LER)两个功能,可以大大减轻纯SCVD架构的低能量利用率问题。DOI会提高电路在产生脉冲上升沿时的能量效率(图3(a)),LER会回收在脉冲下降沿产生过程中容性负载上的能量,从而提高整体能量效率(图3(b))。

图2高压脉冲发生器电路框图

图3动态输出阻抗(DOI)和负载能量回收(LER)原理

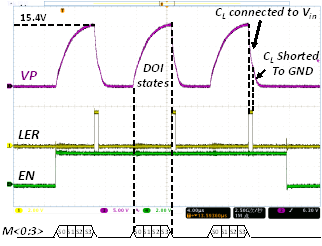

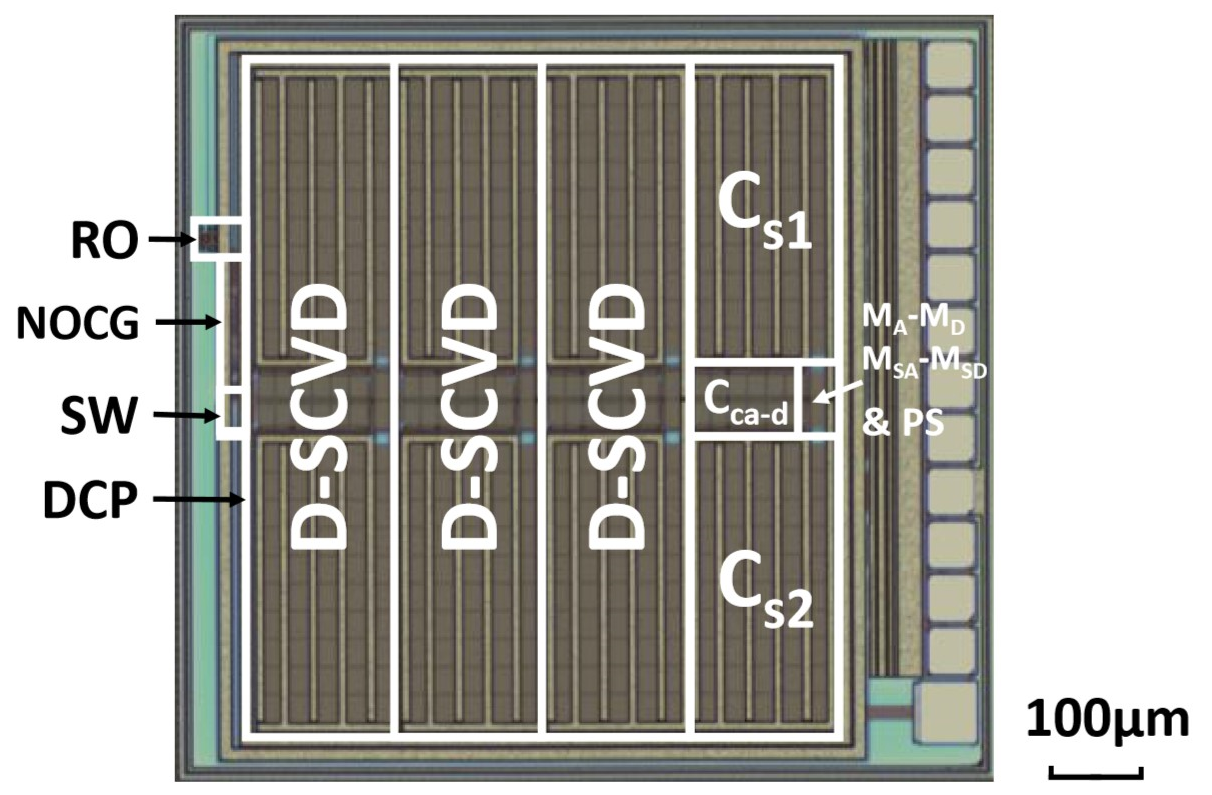

姚镭教授团队设计的全集成式高压脉冲发生器不需要外部元件,输入电源电压3.3V,可实现最大15.4V的脉冲电压和510 kHz的脉冲频率(图4)。在典型的40 kHz脉冲频率下,电路可以支持高达4.8 nF的负载电容;基于DOI和LER两个创新功能,该电路在250 kHz脉冲频率下端到端能量效率可达43.5%;此外,该高压脉冲发生器可以实现9.8 nW的超低待机功率和从待机到输出高压脉冲的零延迟,非常适用于低功耗事件驱动型应用。同时,与其他同类研究工作相比,姚镭教授团队提出的高压脉冲发生器设计突破了标准CMOS工艺中晶体管的标称电压,利用标准CMOS工艺中的寄生器件实现15.4V高压脉冲输出。该电路芯片面积为700μm x800μm,在中芯国际0.18μmCMOS标准工艺下设计并流片制造(图5)。

图4高压脉冲发生器功能测试-脉冲输出波形

图5高压脉冲发生器IC显微照片(SMIC 018标准CMOS工艺)

姚镭教授为共同通讯作者。论文的第一作者为姚镭教授团队联合培养的在读博士曾学韬。

论文链接:https://ieeexplore.ieee.org/document/9296245/authors#authors

(编辑:王治宜,审核:古元冬)